在波士顿的Co乐动滚球app下载msol会议上,LAM Research Corporation举行了关于摩尔定律及其在计算建模中的作用的主题演讲。主题演讲介绍了摩尔的法律如何影响模拟工具的发展,还如何影响这些工具的开发如何允许摩尔的定律实现。这个概念让我感兴趣,我知道这也一直在许多电气工程师的脑海中。例如,当浏览十一月发行时IEEE光谱,我遇到了一篇文章,讨论了摩尔法律的现状,并推测了未来几年的变化。

![]()

硅片。图像归因:大卫·卡伦(David Carron)在En.Wikipedia。

少数是“摩尔”

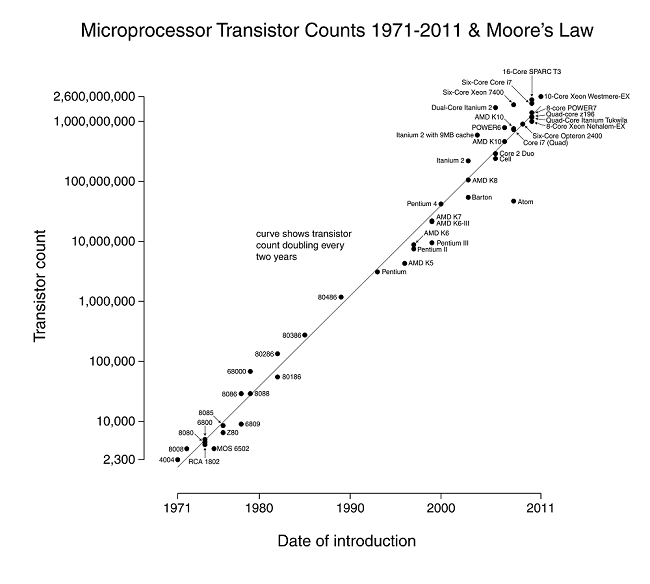

摩尔的定律以英特尔联合创始人戈登·摩尔(Gordon Moore)的名字命名,并指他在1960年代所做的预测,即计算能力将每两年翻一番。到目前为止,这一预测已经实现。根据信息技术和创新基金会的说法,“计算能力今天比40年前快110万倍。”这意味着“少”设备(即较小的笔记本电脑,电话,摄像头等)可以为其尺寸传递“摩尔”(PANDON)功率。在过去的几十年中,该法律已被证明是准确的,以至于它被谈论的是“自然法则”。摩尔定律的几乎不可思议的成果可以归因于以下事实:半导体行业设定行业目标。但是,如IEEE光谱文章,我们衡量摩尔定律的成功的方式已经变得复杂,并且在过去十年的过程中发生了巨大变化。

针对其引言日期绘制的集成电路的晶体管计数(单击图像以放大)。

图像归因:WGSimon。

衡量摩尔定律

目前,摩尔的定律是按可以包含在集成电路中的晶体管数“测量”的。根据IEEE的文章,芯片过去可以用他们的描述节点名称,这反映了集成电路上晶体管的密度和数量,从而反映了摩尔定律从一代到另一代的摩尔定律的发展。但是,在过去的十年中,这些节点名称开始越来越少。实际上,文章建议甚至可以选择节点名称只是为了反映下一代晶体管的位置应该是。因此,与其基于钥匙芯片尺寸的节点名称,例如晶体管的大小和密度,晶体管栅极长度和金属半螺距,而是根据行业期望来给出设备的名称下一个。

使用与过去相同的技术,当前的芯片密度(大多数约为20 nm至22 nm)不再会变小。这是因为随着芯片的变化,必须开发新的制造过程,进而为图案过程增加额外的成本。较小的芯片密度甚至可能需要使用其他芯片特征来补偿随着晶体管变得越来越近并相互作用时出现的并发症。文章指出,由于容纳功能所需的额外空间,这些添加的功能通常会否定芯片大小的总体减小。

半导体行业以几种不同的方式对此做出了回应。本文中给出的一个示例是指Globalfoundries(世界第二大芯片制造商)的新晶体管系列,预计将于2014年开始生产。他们的新综合电路已被命名14纳米芯片,因为这是该公司当前20 nm芯片之后的预期步骤。但是,芯片的密度基本上与20 nm芯片的密度相同。那么这个名字更改是什么?正如文章所述,Globalfoundaries表示,它们称它们为14 nm芯片,因为与以前的芯片相比,它们代表了全代性能的一步。GlobalFoundries没有缩小晶体管大小,而是专注于创建表现下一代性能的设备,而不是晶体管密度的下一步。

尽管这是一家公司对晶体管行业现状的回应,但其他公司仍在试图达到这一趋势。Nearing the end of Moore’s law isn’t a new topic of discussion — for decades we’ve repeatedly thought we had reached the end of our ability to decrease transistor size, only to find that a new patterning process or technological advancement that allowed the trend to continue on to the next generation.

你怎么认为?我们是否达到了“收缩的末端”,还是有更多的晶体管密度改善以使线路下降?

评论(0)